字节序

字节序,又称端序,尾序,英文:Endianness。在计算机科学领域中,字节序是指存放多字节数据的字节(byte)的顺序,典型的情况是整数在内存中的存放方式和网络传输的传输顺序。Endianness有时候也可以用指位序(bit)。

一般而言,字节序指示了一个UCS-2字符的哪个字节存储在低地址。如果LSByte在MSByte的前面,即LSB为低地址,则该字节序是小端序;反之则是大端序。在网络编程中,字节序是一个必须被考虑的因素,因为不同的处理器体系可能采用不同的字节序。在多平台的代码编程中,字节序可能会导致难以察觉的bug。

endian词源

“endian”一词来源于乔纳森·斯威夫特的小说格列佛游记。小说中,小人国为水煮蛋该从大的一端(Big-End)剥开还是小的一端(Little-End)剥开而争论,争论的双方分别被称为Big-endians和Little-endians。

1980年,Danny Cohen在其著名的论文”On Holy Wars and a Plea for Peace“中为平息一场关于字节该以什么样的顺序传送的争论而引用了该词。

基本的字节序

对于单一的字节(a byte),大部分处理器以相同的顺序处理位元(bit),因此单字节的存放方法和传输方式一般相同。

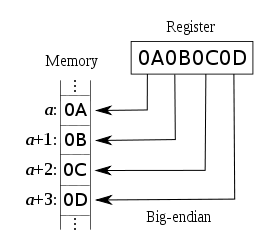

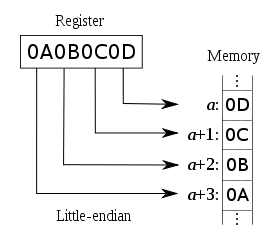

对于多字节数据,如整数(32位机中一般占4字节),在不同的处理器的存放方式主要有两种,以内存中0×0A0B0C0D的存放方式为例,分别有以下几种方式:

- 注: 0x前缀代表十六进制。

大端序

大端序(英:big-endian)或称大尾序。

![]()

- 数据以8bit为单位:

| 地址增长方向 → | |||||

| … | 0×0A | 0×0B | 0×0C | 0×0D | … |

示例中,最高有效位(MSB, Most Significant Byte)是0×0A 存储在最低的内存地址处。下一个字节0×0B存在后面的地址处。正类似于十六进制字节从左到右的阅读顺序。

- 数据以16bit为单位:

| 地址增长方向 → | |||||

| … | 0×0A0B | 0×0C0D | … | ||

最高的16bit单元0×0A0B存储在低位。

小端序

小端序(英:little-endian)或称小尾序。

![]()

- 数据以8bit为单位:

| 地址增长方向 → | |||||

| … | 0×0D | 0×0C | 0×0B | 0×0A | … |

最低有效位(LSB,Least Significant Byte)是0×0D 存储在最低的内存地址处。后面字节依次存在后面的地址处。

- 数据以16bit为单位:

| 地址增长方向 → | |||||

| … | 0×0C0D | 0×0A0B | … | ||

最低的16bit单元0×0C0D存储在低位。

- 更改地址的增长方向:

当更改地址的增长方向,使之由右至左时,表格更具有可阅读性。

| ← 地址增长方向 | |||||

| … | 0×0A | 0×0B | 0×0C | 0×0D | … |

最低有效位(LSB)是0×0D 存储在最低的内存地址处。后面字节依次存在后面的地址处。

| ← 地址增长方向 | |||||

| … | 0×0A0B | 0×0C0D | … | ||

最低的16bit单元0×0C0D存储在低位。

混合序

混合序(英:middle-endian)具有更复杂的顺序。以PDP-11为例,0×0A0B0C0D被存储为:

- 32bit在PDP-11的存储方式

| 地址增长方向 → | |||||

| … | 0×0B | 0×0A | 0×0D | 0×0C | … |

可以看作最高的16bit位和低位以大端序存储,但16bit内部以小端存储。

处理器体系

- x86,MOS Technology 6502,Z80,VAX,PDP-11等处理器为Little endian。

- Motorola 6800,Motorola 68000,PowerPC 970,System/370,SPARC(除V9外)等处理器为Big endian。

- ARM, PowerPC (除PowerPC 970外), DEC Alpha, SPARC V9, MIPS, PA-RISC and IA64的字节序是可配置的。

网络序

网络传输一般采用大端序,也被称之为网络字节序,或网络序。IP协议中定义大端序为网络字节序。

伯克利socket API定义了一组转换函数,用于16和32bit整数在网络序和本机字节序之间的转换。htonl,htons用于本机序转换到网络序;ntohl,ntohs用于网络序转换到本机序。

位序

一般用于描述串行设备的传输顺序。一般硬件传输采用小端序(先传低位),但I2C协议采用大端序。网络协议中只有数据链路层的底端会涉及到。

评论 (0)

评论 (0)